CPLD - Complex Programmable Logic Devices CPLD - MAX V 440 Macro 74 IOs

이미지는 참고용입니다..

제품 세부정보는 제품 사양을 참조하세요.

CPLD - Complex Programmable Logic Devices CPLD - MAX V 440 Macro 74 IOs

$200 이상 주문 시 한정판 중국 스타일 선물을 받으실 수 있습니다..

1000달러 이상 주문 시 배송비 30달러가 면제됩니다..

$5000 이상 주문 시 배송비 및 거래 수수료가 면제됩니다..

이 혜택은 신규 고객과 기존 고객 모두에게 적용되며 2024년 1월 1일부터 2024년 12월 31일까지 유효합니다..

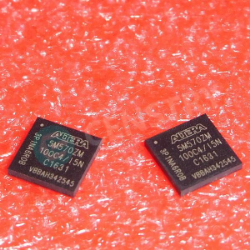

Altera

5M570ZM100I5N datasheet

MBGA100

IC 칩

Lead free/RoHS Compliant

Lead free/RoHS Compliant

지금 견적 요청을 제출하시면 1년 이내에 견적을 제공해 드릴 예정입니다. 7월 02, 2024. 지금 주문하시면 이내에 거래가 완료될 것으로 예상됩니다. 7월 05, 2024. Ps:시간은 GMT+8:00 기준입니다.

Altera

4000 PCS

EP4CE15E22C8N .PDF

Altera

1 PCS

EP3C16E144I7N .PDF

Altera

2000 PCS

EPM240T100I5N .PDF

Altera

2470 PCS

ES1030QI .PDF

2024-07-01

High quality suppliers.

2024-07-01

CENSTRY offers fast service, good pricing and good parts. Dale, Nick, Steve and Andrew are a true credit to our industry.

2024-06-30

Jen is wonderful and great to deal with

2024-06-29

Censtry is honest, reliable and professional.Great doing business with you. Thank you!

2024-06-27

Maryann Chuang is a nice lady!!! Good telephone phone skills and good attitue.

2024-06-23

Censtry Electronics is a wonderful customer! Jim is the best, very prefessional with fast shipping, hope to work more in the future!

2024-06-15

One of the good companies in China to provide good quality, original parts. always pleasure dealing with mike...

2024-05-30

perfect Sales team with perfect support, thanks

2024-04-28

Professional and reliable company.

2024-02-24

Quick response and on time delivery !

우리는 귀하의 피드백을 매우 소중하게 생각합니다. 가장 솔직한 리뷰를 공유해주세요.

*코멘트를 게시하기 전에 계정에 로그인하세요